(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4313168号 (P4313168)

(45) 発行日 平成21年8月12日 (2009.8.12)

(24) 登録日 平成21年5月22日(2009.5.22)

(51) Int. Cl. FL

B81B 5/00 (2006, 01) B81B 5/00 B81C 1/00 (2006, 01) B81C 1/00 GO2B 26/08 (2006.01) GO2B 26/08

> 請求項の数 7 (全 20 頁)

特願2003-403420 (P2003-403420) (21) 出願番号 (22) 出願日 平成15年12月2日(2003.12.2) (65) 公開番号 特開2005-161463 (P2005-161463A) (43) 公開日 平成17年6月23日 (2005.6.23) 審査請求日 平成17年7月4日(2005.7.4)

(出願人による申告) 国等の委託研究の成果に係る特許 出願(平成15年度通信・放送機構、研究テーマ「自律 分散型無線ネットワークの研究開発」に関する委託研究 ||(72)発明者 久保田 和芳 、産業活力再生特別措置法第30条の適用を受けるもの

||(73)特許権者 393031586

$\mathbf{E}$

株式会社国際電気通信基礎技術研究所 京都府相楽郡精華町光台二丁目2番地2

(74)代理人 100098305

弁理士 福島 祥人

(72) 発明者 パブロ・バッカロ

京都府相楽郡精華町光台二丁目2番地2 株式会社国際電気通信基礎技術研究所内

京都府相楽郡精華町光台二丁目2番地2 株式会社国際電気通信基礎技術研究所内

審査官 太田 良隆

最終頁に続く

# (54) 【発明の名称】半導体装置およびその製造方法

# (57)【特許請求の範囲】

# 【請求項1】

### 基板と、

前記基板上に設けられた積層構造とを備え、

前記積層構造は、第1の層、第2の層および第3の層を順に含み、かつ線状の第1の境 界部を介して互いに隣接する第1および第2の領域を有し、

前記第2の領域は、線状の複数の第2の境界部を介して複数の領域にさらに区分され、 前記第2の層は、異なる格子定数を有する複数の半導体層を含み、

前記積層構造の前記第1の領域上および前記第2の領域上にそれぞれ第1および第2の 対向電極が設けられ、

前記第1の境界部を除いて前記第2の領域を取り囲む周辺部における前記第3の層、前 記第2の層および前記第1の層の部分が除去され、前記第2の領域における前記第1の層 の部分が選択的に除去されることにより、前記第2の領域における前記第2の層および前 記第3の層の部分が前記基板から離間し、

前記第2の層に起因する歪により、前記第1の境界部における前記第2の層の部分が谷 状に折曲され、前記複数の第2の境界部における前記第2の層の部分が谷状または山状に 折曲されることにより、前記第1の対向電極と前記第2の対向電極とが平行移動可能に対 向することを特徴とする半導体装置。

# 【請求項2】

前記第1の境界部と前記複数の第2の境界部とは互いに略平行に設けられ、前記第1の対

向電極と前記第2の対向電極とが前記第1の<u>境界部</u>および前記複数の第2の<u>境界部</u>に対して略垂直な方向に平行移動可能に設けられたことを特徴とする請求項1記載の半導体装置

# 【請求項3】

前記複数の第2の<u>境界部</u>のうち少なくとも1つは、前記第1の<u>境界部</u>に対して略垂直に設けられ、

前記第2の領域の一部<u>の領域</u>は前記基板に対して略垂直に起立し、前記第2の対向電極は、前記基板に対して略垂直な軸を中心とする円周方向に回動可能かつ前記第1の対向電極に対して平行移動可能に設けられたことを特徴とする請求項1記載の半導体装置。

### 【請求項4】

前記第 1 の 境界部 および前記複数の第 2 の 境界部 において少なくとも前記第 3 の層 の部分が除去されることにより 前記第 1 の境界部における前記第 2 の層の部分が谷状に折曲され 前記複数の第 2 の 境界部における前記第 2 の層の部分 が谷状または山状に折曲されることを特徴とする請求項 1 ~ 3 のいずれかに記載の半導体装置。

## 【請求項5】

前記第2の層は、第1の格子定数を有する第1の半導体層と、前記第1の格子定数よりも 小さい第2の格子定数を有する第2の半導体層とを含み、

前記第1の<u>境界部</u>および前記複数の第2の<u>境界部における</u>前記第2の層<u>の部分</u>が谷状に 折曲されるように前記第1の<u>境界部</u>および前記複数の第2の<u>境界部における</u>前記第3の層 の部分が除去されたことを特徴とする請求項1~4のいずれかに記載の半導体装置。

### 【請求項6】

前記第2の層は、第1の格子定数を有する第1の半導体層と、前記第1の格子定数よりも小さい第2の格子定数を有する第2の半導体層と、前記第2の格子定数よりも大きい第3の格子定数を有する第3の半導体層とを含み、

前記複数の第2の<u>境界部</u>のうち少なくとも1つの第2の<u>境界部における</u>前記第2の層<u>の</u>部分が山状に折曲されるように前記少なくとも1つの第2の<u>境界部における</u>前記第3の層の部分が除去され、前記第1の<u>境界部</u>および前記複数の第2の<u>境界部</u>のうち他の第2の<u>境界部における</u>前記第2の層<u>の部分</u>が谷状に折曲されるように前記第1の<u>境界部</u>および前記他の第2の<u>境界部における</u>前記第3の層<u>の部分</u>および前記第3の半導体層<u>の部分</u>が除去されたことを特徴とする請求項1~4のいずれかに記載の半導体装置。

### 【請求項7】

基板上に第1の層、第2の層および第3の層を順に含む積層構造を形成するステップを備え、

前記積層構造は、線状の第1の境界部を介して互いに隣接する第1および第2の領域を 有し、

前記第2の領域は、線状の複数の第2の境界部を介して複数の領域にさらに区分され、前記第2の層は、異なる格子定数を有する複数の半導体層を含み、

前記積層構造の前記第1の領域上および前記第2の領域上にそれぞれ第1および第2の対向電極を設けるステップと、

前記第1の<u>境界部</u>を除<u>いて</u>前記第2の領域を<u>取り囲む周辺部における</u>前記第3の層、前記第2の層および前記第1の層の部分を除去するステップと、

前記第2の領域における前記第1の層<u>の部分</u>を選択的に除去することにより、前記第2の領域における前記第2の層および前記第3の層<u>の部分</u>を前記基板から離間させ、前記第2の層に起因する歪により、前記第1の境界部における前記第2の層の部分を谷状に折曲させ、前記複数の第2の境界部における前記第2の層の部分を谷状または山状に折曲させることにより、前記第1の対向電極と前記第2の対向電極とを平行移動可能に対向させるステップとをさらに備えたことを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

# 【技術分野】

[0001]

10

20

30

本発明は、起立構造を有する半導体装置およびその製造方法に関する。

# 【背景技術】

## [00002]

起立構造を有するマイクロ光学ベンチが、シリコンを用いたMEMS(マイクロエレクトロ・メカニカル・システム)技術により実現されている。このMEMS技術を用いて、例えば、レーザ走査ディスプレイのための共振マイクロスキャナ、可動マイクロ反射器、半導体レーザの外部共振器のための走査マイクロミラー等を作製することが報告されている。

# [0003]

この従来のMEMS技術では、積層された半導体層の一部をエッチングにより剥離させた後、剥離した部分をスライドさせて起立させるとともにヒンジで接合することにより、起立構造を形成している。この起立構造を用いて基板上に所定の角度で起立したミラーが構成される。このようなミラーは、くし型ドライバ(comb driver)またはスライディング機構により操作される。

### [0004]

しかしながら、従来のMEMS技術を用いて半導体により起立構造を作製する場合、剥離した半導体層をスライドさせる際に磨耗が生じる。また、半導体層を所定の位置まで正確にスライドさせることは困難である。そのため、起立構造を構成する各部材の角度および位置を正確に制御することが困難であるとともに、作業性が悪い。

## [00005]

一方、本発明者らは、格子定数の異なる複数の半導体層の積層構造を用いて起立構造を 有する半導体装置を製造する方法を提案している(特許文献 1 参照)。

【特許文献1】特開2001-260092号公報

【発明の開示】

【発明が解決しようとする課題】

## [0006]

上記の半導体装置およびその製造方法によれば、起立構造を構成する各部材の角度および位置を正確に制御することができる。

# [0007]

そこで、この方法を用いて光学スキャナ、アクチュエータ等の種々の装置に応用可能な 半導体装置を容易に作製することが望まれる。特に、1対の部分が互いに平行移動可能な 構造を容易に作製することが望まれる。

#### [00008]

本発明の目的は、1対の部分が互いに平行移動可能な構造を有し、容易かつ正確に作製することができるとともに小型化が可能な半導体装置およびその製造方法を提供することである。

【課題を解決するための手段】

## [0009]

第1の発明に係る半導体装置は、<u>基板</u>と、基板上に設けられた積層構造とを備え、積層構造は、第1の層、第2の層および第3の層を順に含み、<u>かつ線状の第1の境界部を介して互いに隣接する第1および第2の領域を有し、第2の領域は、線状の複数の第2の境界部を介して複数の領域にさらに区分され、</u>第2の層は、異なる格子定数を有する複数の半導体層を含<u>み、積層構造の</u>第1の領域上および第2の領域上にそれぞれ第1および第2の対向電極が設けられ、第1の境界部を除いて第2の領域を取り囲む周辺部における第3の層、第2の層および第1の層<u>の部分</u>が除去され、第2の領域における第1の層<u>の部分</u>が選択的に除去されることにより、第2の領域における第2の層および第3の層の部分が登板から離間し、第2の層に起因する歪により、第1の境界部における第2の層の部分が谷状または山状に折曲されることにより、第1の対向電極と第2の対向電極とが平行移動可能に対向するものである。

#### [0010]

50

20

10

30

20

30

40

50

本発明に係る半導体装置においては、第1の<u>境界部</u>を除いて第2の領域を取り囲む<u>周辺部における</u>第3の層、第2の層および第1の層<u>の部分</u>が除去され、第2の領域における第1の層<u>の部分</u>が選択的に除去される。それにより、第2の領域における第2の層および第3の層の部分が基板から離間する。また、第2の層に起因する歪により<u>、第1の境界部における第2の層の部分が谷状に折曲され、複数の第2の境界部における第2の層の部分が谷状または山状に折曲される。それにより、第1の対向電極と第2の対向電極とが平行移動可能に対向する。</u>

# [0011]

この場合、第1の対向電極と第2の対向電極との間に電圧を印加することにより、第1の対向電極と第2の対向電極との間に静電力が働く。それにより、第1の対向電極と第2の対向電極とを平行移動させ、第2の領域の各部分を移動させることが可能となる。

[0012]

また、第2の層における複数の半導体層の格子定数の差に起因する歪を緩和するように 第1の境界部 および複数の第2の<u>境界部における第2の層の部分が</u>谷状または山状に折曲 されるので、手動組み立てまたは複雑な組み立て機構を必要とすることなく第1の対向電 極と第2の対向電極とが平行移動可能な構造を容易かつ正確に作製することが可能になる とともに、半導体装置の小型化が可能になる。

### [0013]

第1の<u>境界部</u>と複数の第2の<u>境界部</u>とは互いに略平行に設けられ、第1の対向電極と第2の対向電極とが第1の<u>境界部</u>および複数の第2の<u>境界部</u>に対して略垂直な方向に平行移動可能に設けられてもよい。

[0014]

この場合、互いに略平行に設けられた第1の<u>境界部および</u>複数の第2の<u>境界部における第2の層の部分</u>が谷状または山状に折曲されることにより、第1の対向電極と第2の対向電極とが第1の<u>境界部</u>および複数の第2の<u>境界部</u>に対して略垂直な方向に平行移動可能となる。それにより、第2の領域の各部分を直線状に移動させることができる。

[0015]

複数の第2の<u>境界部</u>のうち少なくとも1つは、第1の<u>境界部</u>に対して略垂直に設けられ、第2の領域の一部<u>の領域</u>は基板に対して略垂直に起立し、第2の対向電極は、基板に対して略垂直な軸を中心とする円周方向に回動可能かつ第1の対向電極に対して平行移動可能に設けられてもよい。

[0016]

この場合、複数の第2の<u>境界部</u>のうち少なくとも1つが第1の<u>境界部</u>に対して略垂直に設けられることにより、第2の領域の一部<u>の領域</u>が基板に対して略垂直に起立する。それにより、第2の対向電極を基板に対して略垂直な軸を中心とする円周方向に回動させるとともに第1の対向電極に対して平行移動させ、第2の領域の各部分を円周方向に沿って移動させることが可能となる。

[0017]

第 1 の<u>境界部</u>および複数の第 2 の<u>境界部</u>において少なくとも第 3 の層<u>の部分</u>が除去されることにより第 1 の境界部における第 2 の層の部分が谷状に折曲され、複数の第 2 の境界部における第 2 の層の部分が谷状または山状に折曲されてもよい。

[0018]

この場合、第1の<u>境界部</u>および複数の第2の<u>境界部における</u>第3の層<u>の部分</u>が除去されると、第2の層における第1、第2および第3の半導体層の第1、第2および第3の格子定数の差に起因する歪を緩和するように第2の層が第1の<u>境界部における第2の層の部分が</u>谷状または山状に折曲される。

[0019]

第2の層は、第1の格子定数を有する第1の半導体層と、第1の格子定数よりも小さい 第2の格子定数を有する第2の半導体層とを含み、第1の境界部および複数の第2の境界

20

30

40

50

<u>部における</u>第2の層<u>の部分</u>が谷状に折曲されるように第1の<u>境界部</u>および複数の第2の<u>境</u> 界部における第3の層の部分が除去されてもよい。

## [0020]

この場合、第1の<u>境界部</u>および複数の第2の<u>境界部における</u>第3の層<u>の部分</u>が除去されることにより、第1の半導体層の第1の格子定数と第2の半導体層の第2の格子定数との差に起因する歪を緩和するように第1の<u>境界部</u>および複数の第2の<u>境界部における</u>で第2の層の部分が谷状に折曲される。

# [0021]

第2の層は、第1の格子定数を有する第1の半導体層と、第1の格子定数よりも小さい第2の格子定数を有する第2の半導体層と、第2の格子定数よりも大きい第3の格子定数を有する第3の半導体層とを含み、複数の第2の境界部のうち少なくとも1つの第2の境界部における第2の層の部分が山状に折曲されるように少なくとも1つの第2の境界部における第3の層の部分が除去され、第1の境界部および複数の第2の境界部のうち他の第2の境界部における第2の層の部分が谷状に折曲されるように第1の境界部および他の第2の境界部における第3の層の部分および第3の半導体層の部分が除去されてもよい。

# [0022]

この場合、少なくとも1つの第2の<u>境界部における</u>第3の層<u>の部分</u>が除去されることにより、第1、第2および第3の半導体層の第1、第2および第3の格子定数の差に起因する歪を緩和するように少なくとも1つの第2の<u>境界部における</u>第2の層<u>の部分</u>が山状に折曲される。また、第1の<u>境界部</u>および複数の第2の<u>境界部</u>のうち他の第2の<u>境界部における</u>第3の層<u>の部分</u>および第3の半導体層<u>の部分</u>が除去されることにより、第1の半導体層の第1の格子定数と第2の半導体層の第2の格子定数との差に起因する歪を緩和するように第1の境界部および他の第2の境界部における第2の層の部分が谷状に折曲される。

#### [0023]

第2の発明に係る半導体装置の製造方法は、基板上に第1の層、第2の層および第3の層を順に含む積層構造を形成するステップを備え、積層構造は、線状の第1の境界部を介して互いに隣接する第1および第2の領域を有し、第2の領域は、線状の複数の第2の境界部を介して複数の領域にさらに区分され、第2の層は、異なる格子定数を有する複数の半導体層を含み、積層構造の第1の領域上および第2の領域上にそれぞれ第1および第2の対向電極を設けるステップと、第1の境界部を除いて第2の領域を取り囲む周辺部における第3の層、第2の層および第1の層の部分を除去するステップと、第2の領域における第1の層の部分を選択的に除去することにより、第2の領域における第2の層の部分を選択的に除去することにより、第2の領域における第2の層の部分を谷状に折曲させ、第2の層に起因する歪により、第1の境界部における第2の層の部分を谷状に折曲させ、複数の第2の境界部における第2の層の部分を谷状または山状に折曲させることにより、第1の対向電極と第2の対向電極とを平行移動可能に対向させるステップとをさらに備えたものである。

# [0024]

本発明に係る半導体装置の製造方法においては、第1の<u>境界部</u>を除<u>いて</u>第2の領域を取り囲む<u>周辺部における</u>第3の層、第2の層および第1の層<u>の部分</u>が除去され、第2の領域における第1の層<u>の部分</u>が選択的に除去される。それにより、第2の領域における第2の層および第3の層の部分が基板から離間する。また、第2の層に起因する歪により<u>、第1</u>の境界部における第2の層の部分が谷状に折曲され、複数の第2の境界部における第2の層の部分が谷状に折曲され、複数の第2の境界部における第2の層の部分が谷状または山状に折曲される。それにより、第1の対向電極と第2の対向電極とが平行移動可能に対向する。

#### [0025]

この場合、第1の対向電極と第2の対向電極との間に電圧を印加することにより、第1の対向電極と第2の対向電極との間に静電力が働く。それにより、第1の対向電極と第2の対向電極とを平行移動させ、第2の領域の各部分を移動させることが可能となる。

# [0026]

また、第2の層における複数の半導体層の格子定数の差に起因する歪を緩和するように

第1の境界部および複数の第2の境界部における第2の層の部分が谷状または山状に折曲 されるので、手動組み立てまたは複雑な組み立て機構を必要とすることなく第1の対向電 極と第2の対向電極とが平行移動可能な構造を容易かつ正確に作製することが可能になる とともに、半導体装置の小型化が可能になる。

## 【発明の効果】

# [0027]

本発明によれば、第1の対向電極と第2の対向電極とを平行移動させ、第2の領域の各 部分を移動させることが可能となる。また、手動組み立てまたは複雑な組み立て機構を必 要とすることなく第1の対向電極と第2の対向電極とが平行移動可能な構造を容易かつ正 確に作製することが可能になるとともに、半導体装置の小型化が可能になる。

# 【発明を実施するための最良の形態】

#### [0028]

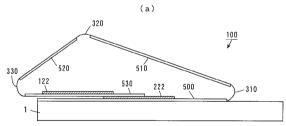

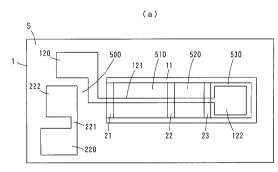

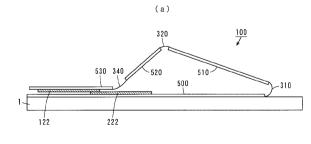

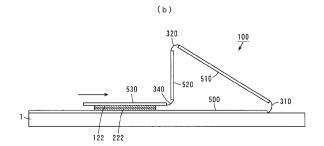

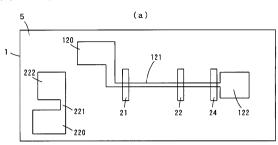

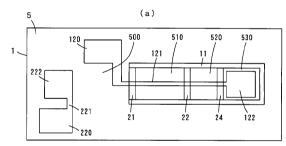

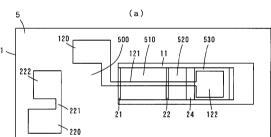

図 1 ( a ) , ( b ) は本発明の第 1 の実施の形態における半導体装置の構成および動作 を説明するための模式的断面図である。

# [0029]

図1において、基板1上のプレート500にヒンジ310を介して矩形のプレート51 0が連結され、プレート510にヒンジ320を介して矩形のプレート520が連結され 、プレート520にヒンジ330を介して矩形のプレート530が連結されている。

## [0030]

プレート500上に矩形の静電板222が設けられ、プレート530上に矩形の静電板 122が設けられている。

20

10

#### [0031]

ヒンジ310,320,330は谷状に折曲される。それにより、プレート530とプ レート 5 0 0 とが対向し、静電板 1 2 2 と静電板 2 2 2 とがプレート 5 3 0 を介して対向 する。

# [0032]

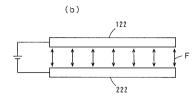

通常は、図1(a)に示すように、プレート530とプレート500とが部分的に対向 するように設定されている。それにより、静電板122と静電板222とが部分的に対向 する。後述するように、静電板122と静電板222との間に電圧が印加されると、静電 板122と静電板222との間に静電力が作用する。それにより、図1(b)に示すよう に、静電板122と静電板222とが全体的に対向するように矢印の方向にプレート53 0がプレート500に対して平行移動する。

30

### [0033]

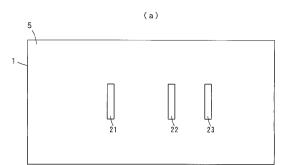

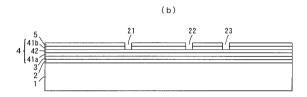

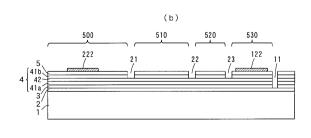

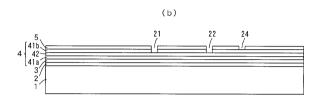

図2~図6は図1の半導体装置100の製造方法を示す工程図であり、(a)は模式的 平面図、(b)は模式的断面図である。

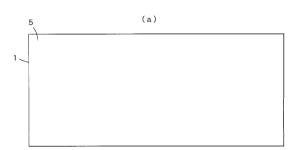

#### [0034]

まず、図2に示すように、GaAsからなる基板1上に、GaAsからなるバッファ層 2、AlGaAsからなる犠牲層(sacrificial層)3、歪層(strain層)4および構成 要素層(component層) 5 を順にエピタキシャル成長させる。 これらのバッファ層 2、 犠牲層3、歪層4および構成要素層5は、MBE法(分子線エピタキシャル成長法)、M OCVD法(有機金属化学的気相成長法)、CVD法(化学的気相成長法)等のエピタキ シャル成長技術を用いて形成される。

40

# [0035]

歪層4は、厚さ数nm~数十nmの第1のInGaAs層41a、厚さ数nm~数十n mのGaAs層42および厚さ数nm~数十nmの第2のInGaAs層41bにより構 成される。本実施の形態では、第1および第2のInGaAs層41a,41bの格子定 数は、GaAs層42の格子定数よりも大きい。そのため、歪層4に格子定数の差による 歪が発生する。 歪層 4 の働きについては後述する。

# [0036]

また、構成要素層 5 は、分布反射膜 (Distributed Bragg Reflector:以下、 D B R 膜と

呼ぶ)により構成される。 D B R 膜は、複数の A 1 G a A s 層と複数の G a A s 層とが交互に積層されてなる積層構造を有する。 A 1 G a A s 層および G a A s 層の周期は例えば  $4\sim2$ 0 である。

### [0037]

なお、A1Asを酸化することにより得られる酸化アルミニウム層とA1GaAs層とを交互に積層することにより構成要素層5を構成してもよい。また、構成要素層5がGaAsプレートからなってもよい。

# [0038]

なお、歪層 4 と構成要素層 5 との間に、例えば厚さ 1 5 0 n mの A  $1_{0.58}$  G  $a_{0.42}$  A s からなるエッチング停止層を設けてもよい。また、構成要素層 5 上に、例えば厚さ 1 0 n mの I n G a A s からなる歪補償層(strain compensation層)および例えば厚さ 1 0 n mの G a A s からなるキャップ層を設けてもよい。歪補償層は、後の工程で剥離された構成要素層 5 の変形を防止するために設けられる。キャップ層は、製造工程時における I n G a A s 中の I n の蒸発を防止するために設けられる。

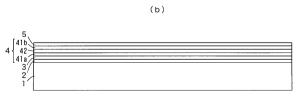

### [0039]

次に、図3に示すように、フォトリソグラフィおよびエッチングにより構成要素層5および第2のInGaAs層41bを除去し、後述するヒンジ310,320,330を規定する谷折溝21,22,23を間隔をおいて互いに平行に形成する。エッチングとしては、ウェットエッチング法またはドライエッチング法を用いることができる。

# [0040]

次に、図4に示すように、構成要素層5上に、金属膜からなる配線層121,221を形成する。また、構成要素層5上に金属膜からなる電極パッド120,220および静電板122,1により電極パッド120と静電板122とが電気的に接続され、配線層221により電極パッド220と静電板222とが電気的に接続される。

## [0041]

配線層121は、後述するヒンジ310,320,330と交差するため、電極パッド120,220および静電板122,22に比べて小さな厚みを有する。

# [0042]

本実施の形態の半導体装置100では、静電板122,222に静電力を発生させるために、電極パッド120,220間に電圧が印加されるが、配線層121,221に電流は流れない。そのため、配線層121,221の厚さを薄くすることにより、ヒンジの湾曲が可能になるとともにヒンジの湾曲による配線層121,221の切れを防止することができる。電極パッド120,220は、ワイヤボンディングを確実にするために、ある程度大きな厚みを有することが好ましい。

# [0043]

例えば、配線層121,221は、厚さ4nmのTi(チタン)および厚さ40nmのAu(金)の積層構造からなる。電極パッド120,220および静電板122,222は、厚さ4nmのTiおよび厚さ200nmのAuの積層構造からなる。そのため、薄い配線層121,221の堆積工程は、厚い電極パッド120,220および静電板122,220堆積工程とは別に行われる。

#### [0044]

次に、図5に示すように、谷折溝21を除いて谷折溝21と谷折溝22との間の領域、谷折溝22と谷折溝23との間の領域および静電板122を含む領域の周囲を取り囲むように、フォトリソグラフィおよびエッチングにより構成要素層5、歪層4および犠牲層3を除去し、分離溝11を形成する。それにより、分離溝11で取り囲まれた構成要素層5が周囲の構成要素層5から分離される。この場合にも、エッチングとしてウェットエッチング法またはドライエッチング法を用いる。

# [0045]

その後、図6に示すように、分離溝11で取り囲まれた領域における歪層4下の犠牲層

20

10

30

40

3 をウェットエッチング法により選択的にエッチングする。その結果、歪層 4 を構成する第 1 の I n G a A s 層 4 1 a と G a A s 層 4 2 との格子定数の差に起因する歪を緩和するように歪層 4 がヒンジ 3 1 0 , 3 2 0 , 3 3 0 として谷折溝 2 1 , 2 2 , 2 3 の下方で谷状に湾曲する。それにより、構成要素層 5 が谷折溝 2 1 , 2 2 , 2 3 で谷状に折曲される

[0046]

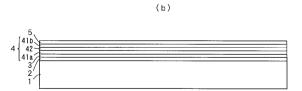

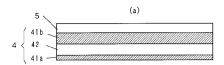

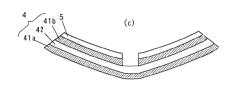

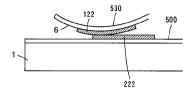

ここで、構成要素層 5 を山折りおよび谷折りする方法について説明する。図 7 は歪層 4 および構成要素層 5 を示す模式的断面図であり、(a)は折曲されていない状態を示し、(b)は山折された状態を示し、(c)は谷折された状態を示す。なお、構成要素層 5 の山折りは、第 2 の実施の形態に係る半導体装置の製造の際に用いられる。

[0047]

図7(a)に示すように、歪層4は、GaAs層42が第1のInGaAs層41aおよび第2のInGaAs層41bにより挟まれた構造を有する。第2のInGaAs層41bは第1のInGaAs層41aよりも大きな厚みを有する。第2のInGaAs層41b上に構成要素層5が形成される。

[0048]

この場合、第1のInGaAs層41aおよび第2のInGaAs層41bはGaAs層42に比べて大きな格子定数を有するので、第1のInGaAs層41aはGaAs層42を上方に湾曲させるように作用し、第2のInGaAs層41bはGaAs層42を下方に湾曲させるように作用する。この状態では、第2のInGaAs層41b上に構成要素層5が形成されているため、歪層4は湾曲しない。

[0049]

図7(b)に示すように、構成要素層5を第2のInGaAs層41bが露出するまでエッチングすると、第1のInGaAs層41aの厚みが第2のInGaAs層41bの厚みに比べて小さいので、第2のInGaAs層41bがGaAs層42を下方に湾曲させるように作用する。それにより、構成要素層5がエッチング部分で山状に折曲される。

[0050]

図7(c)に示すように、構成要素層5および第2のInGaAs層41bをGaAs層42が露出するまでエッチングすると、第1のInGaAs層41aはGaAs層42を上方に湾曲させるように作用する。それにより、構成要素層5がエッチング部分で谷状に折曲される。

[0051]

このように、歪層 4 を用いるとともにエッチング深さを調整することにより、構成要素層 5 を谷状および山状に折曲することができる。

[0052]

この場合、第1および第2のInGaAs層41a,41bの厚さ、GaAs層42の厚さおよび第1および第2のInGaAs層41a,41bにおけるIn組成比を最適に選択することにより、構成要素層5を所望の角度で折曲することができる。

[0053]

例えば、第1のInGaAs層41aの厚さを10nmとし、GaAs層42の厚さを10nmとする。また、第1のInGaAs層41aの組成In $_{\chi}$  Ga $_{1-\chi}$  AsにおけるIn組成比Xを0.2とすると、歪層4が垂直に折曲する。

[0054]

なお、第1のInGaAs層41aにおけるIn組成比を変化させることにより、In GaAsとGaAsとの格子定数の差を約7%まで変化させることができる。

[0055]

第1のIn G a A s 層 4 1 a の厚さ t 1 と G a A s 層 4 2 の厚さ t 2 とが等しいとした場合、第1のIn G a A s 層 4 1 a の厚さ t 1、G a A s 層 4 2 の厚さ t 2、第1のIn G a A s 層 4 1 a におけるIn 組成比 X および歪層 4 の曲率半径 R との間には、次の関係がある。

10

20

30

40

#### [0056]

$R = (a/a) \cdot \{(t1+t2)/2\}$

#### [0057]

上記のようにして、プレート530とプレート500とが平行移動可能に対向する図1の半導体装置100が容易かつ正確に作製される。

#### [0058]

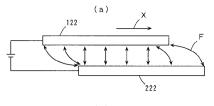

#### [0059]

図8は図1の半導体装置100の動作原理を説明するための図である。図8(a)に示すように、初期状態では、静電板122と静電板222とが部分的に重なった状態で対向している。この状態で、静電板122と静電板222との間に電圧を印加すると、静電板122と静電板22と静電板222に前電大が働く。この場合、静電板122が毎電板122が手電板222に静電板222に対して平行移動し、図8(b)に示すように、静電板122が静電板222に完全に重なる。

# [0060]

静電板122と静電板222との間に印加する電圧を低下させるかまたは0にすると、図1のヒンジ310,320,330の弾性力により、静電板122が静電板222に対して矢印Xと逆方向に平行移動し、図8(a)に示す状態に復帰する。

## [0061]

このように、静電板122と静電板222との間に印加する電圧を変化させることにより、静電板122と静電板222とを直線状に互いに平行移動させ、図1のプレート53 0をプレート500に対して平行移動させることができる。

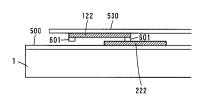

#### [0062]

図 9 は図 1 の半導体装置 1 0 0 においてプレート 5 3 0 とプレート 5 0 0 とのスライド特性を向上させるための第 1 の方法を示す模式的断面図である。また、図 1 0 は図 1 の半導体装置 1 0 0 においてプレート 5 3 0 とプレート 5 0 0 とのスライド特性を向上させるための第 2 の方法を示す模式的断面図である。

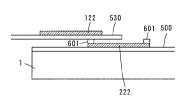

### [0063]

図9の方法では、静電板222上にダイアモンドライクカーボン等からなるコンタクトパッド601が例えば4箇所に形成される。それにより、プレート530と静電板222との摩擦が低減されるとともに、プレート530と静電板222との吸着が防止される。また、プレート530の磨耗が防止され、静電板122と静電板222との間隔が一定に保たれる。

# [0064]

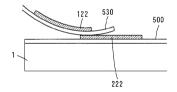

図10の方法では、図7(c)の第2のInGaAs層41bを設けないかまたは第2のInGaAs層41bよりも第1のInGaAs層41aの厚さを大きく形成する。それにより、プレート530がやや湾曲する。この場合、プレート530が静電板222に曲面で接触するので、プレート530と静電板222との摩擦が低減されるとともに、プレート530と静電板222との吸着が防止される。また、プレート530の磨耗が防止され、静電板122と静電板222との間隔が一定に保たれる。

# [0065]

なお、図10の方法においても、図9の方法と同様に、静電板222上にダイアモンドライクカーボン等からなるコンタクトパッドを形成してもよい。

# [0066]

第1の実施の形態の半導体装置100の用途については、後述する。

20

10

30

40

20

30

40

50

#### [0067]

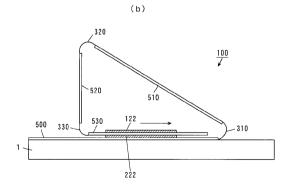

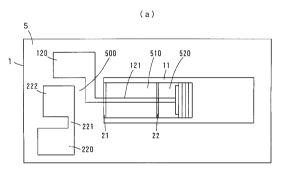

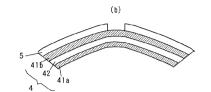

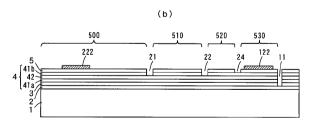

図11(a),(b)は本発明の第2の実施の形態における半導体装置の構成および動作を説明するための模式的断面図である。

### [0068]

図 1 1 において、基板 1 上のプレート 5 0 0 にヒンジ 3 1 0 を介して矩形のプレート 5 1 0 が連結され、プレート 5 1 0 にヒンジ 3 2 0 を介して矩形のプレート 5 2 0 が連結され、プレート 5 2 0 にヒンジ 3 4 0 を介して矩形のプレート 5 3 0 が連結されている。

# [0069]

プレート 5 0 0 上に矩形の静電板 2 2 2 が設けられ、プレート 5 3 0 上に矩形の静電板 1 2 2 が設けられている。

## [0070]

ヒンジ310,320は谷状に折曲され、ヒンジ340は山状に折曲される。それにより、プレート530とプレート500とが対向し、静電板122と静電板222とが対向する。なお、静電板122と静電板222とが電気的に接触しないように、静電板122,22の表面には絶縁膜(図示せず)が形成されている。

#### [0071]

通常は、図11(a)に示すように、プレート530とプレート500とが部分的に対向するように設定されている。それにより、静電板122と静電板222とが部分的に対向する。上述のように、静電板122と静電板222との間に電圧が印加されると、静電板122と静電板222との間に静電力が作用する。それにより、図11(b)に示すように、静電板122と静電板222とが全体的に対向するように矢印の方向にプレート530が平行移動する。

## [0072]

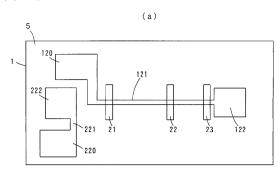

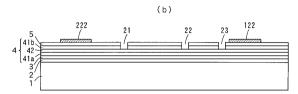

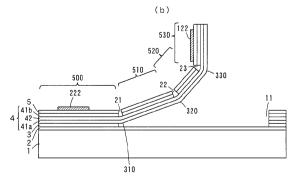

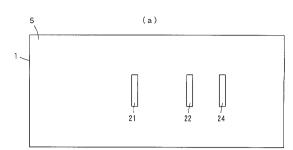

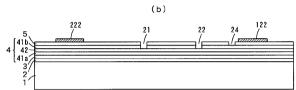

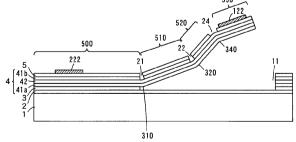

図12~図16は図11の半導体装置100の製造方法を示す工程図であり、(a)は模式的平面図、(b)は模式的断面図である。

# [0073]

まず、図12に示すように、GaAsからなる基板1上に、第1の実施の形態と同様にして、GaAsからなるバッファ層2、A1GaAsからなる犠牲層3、歪層4および構成要素層5を順にエピタキシャル成長させる。

# [0074]

これらのバッファ層 2 、犠牲層 3 、歪層 4 および構成要素層 5 は、MBE法、MOCVD法、CVD法等のエピタキシャル成長技術を用いて形成される。

#### [0075]

歪層4は、厚さ数nm~数十nmの第1のInGaAs層41a、厚さ数nm~数十nmのGaAs層42および厚さ数nm~数十nmの第2のInGaAs層41bにより構成される。本実施の形態では、第1および第2のInGaAs層41a,41bの格子定数は、GaAs層42の格子定数よりも大きい。そのため、歪層4に格子定数の差による歪が発生する。歪層4の働きについては図7を用いて説明した通りである。

# [0076]

また、構成要素層 5 は、DBR膜により構成される。DBR膜の構成は、第1の実施の 形態におけるDBR膜の構成と同様である。また、構成要素層 5 が GaAs プレートから なってもよい。

# [0077]

なお、歪層 4 と構成要素層 5 との間に、例えば厚さ  $150nmoAl_{0.58}Ga_{0.42}As$  からなるエッチング停止層を設けてもよい。また、構成要素層 5 上に、例えば厚さ 10nmoInGaAs からなる歪補償層および例えば厚さ 10nmoGaAs からなるキャップ層を設けてもよい。

### [0078]

次に、図13に示すように、フォトリソグラフィおよびエッチングにより構成要素層5 および第2のInGaAs層41bを除去し、後述するヒンジ310,320を規定する 谷折溝21,22を間隔をおいて互いに平行に形成し、構成要素層5を除去し、山折溝2 4を谷折溝22に対して間隔をおいて平行に形成する。エッチングとしては、ウェットエッチング法またはドライエッチング法を用いることができる。

#### [0079]

次に、図14に示すように、構成要素層5上に、金属膜からなる配線層121,221を形成する。また、構成要素層5上に金属膜からなる電極パッド120,220および静電板122,222を形成する。配線層121により電極パッド120と静電板122とが電気的に接続され、配線層221により電極パッド220と静電板222とが電気的に接続される。

# [0800]

電極パッド120,220、配線層121,221および静電板122,222の形成方法は第1の実施の形態と同様である。さらに、静電板122,222上に絶縁膜(図示せず)を形成する。

# [0081]

次に、図15に示すように、谷折溝21を除いて谷折溝21と谷折溝22との間の領域、谷折溝22と山折溝24との間の領域および静電板122を含む領域の周囲を取り囲むように、フォトリソグラフィおよびエッチングにより構成要素層5、歪層4および犠牲層3を除去し、分離溝11を形成する。それにより、分離溝11で取り囲まれた構成要素層5が周囲の構成要素層5から分離される。この場合にも、エッチングとしてウェットエッチング法またはドライエッチング法を用いる。

### [0082]

その後、図16に示すように、分離溝11で取り囲まれた領域における歪層4下の犠牲層3をウェットエッチング法により選択的にエッチングする。その結果、歪層4を構成する第1および第2のInGaAs層41a,41bとGaAs層42との格子定数の差に起因する歪を緩和するように歪層4がヒンジ310,320として谷折溝21,22の下方で谷状に湾曲し、歪層4がヒンジ340として山折溝24の下方で山状に湾曲する。それにより、構成要素層5が谷折溝21,22で谷状に折曲され、山折溝24で山状に折曲される。

# [0083]

構成要素層 5 を山折りおよび谷折りする方法については、図 7 を用いて説明した通りである。

# [0084]

上記のようにして、プレート530とプレート500とが平行移動可能に対向する図11の半導体装置100が容易かつ正確に作製される。

# [0085]

図11の半導体装置100の動作原理は、図8を用いて説明した図1の半導体装置10 0の動作原理と同様である。

## [0086]

図17は図11の半導体装置100においてプレート530とプレート500とのスライド特性を向上させるための第1の方法を示す模式的断面図である。また、図18は図11の半導体装置100においてプレート530とプレート500とのスライド特性を向上させるための第2の方法を示す模式的断面図である。

#### [0087]

図17の方法では、静電板122上にダイアモンドライクカーボン等からなるコンタクトパッド601が例えば4箇所に形成される。なお、静電板222上にコンタクトパッドを形成してもよい。それにより、静電板122と静電板222との摩擦が低減されるとともに、静電板122と静電板222との吸着が防止される。また、静電板122,222の磨耗が防止され、静電板122と静電板222との間隔が一定に保たれる。

#### [0088]

図 1 8 の方法では、静電板 1 2 2 の側のプレート 5 3 0 の表面に I n G a A s 層が M B

10

20

40

20

30

40

50

E法等により形成される。それにより、プレート530がやや湾曲する。この場合、静電板122が静電板222に絶縁膜を介して曲面で接触するので、静電板122と静電板222との摩擦が低減されるとともに、静電板122と静電板222との間隔が一定に保たれる。

[0089]

なお、図18の方法においても、図17の方法と同様に、静電板122または静電板2 22上にダイアモンドライクカーボン等からなるコンタクトパッドを形成してもよい。

[0090]

次に、第1および第2の実施の形態の半導体装置100の用途について説明する。

[0091]

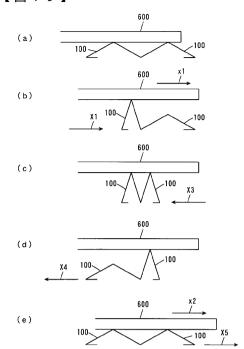

図19は図1の半導体装置100を用いたアクチュエータを示す模式図である。一対または複数対の半導体装置100を用いてアクチュエータが構成される。図19のアクチュエータは、搬送対象物600を搬送する。

[0092]

図19(a)に示すように、搬送方向において前方側の半導体装置100および後方側の半導体装置100上に搬送対象物600が載置される。図19(b)に示すように、後方側の半導体装置100が矢印X1の方向にスライドする。それにより、搬送対象物600が矢印x1で示すように移動する。このとき、搬送対象物600は、後方側の半導体装置100により支持される。

[0093]

次に、図19(c)に示すように、前方側の半導体装置100が矢印×3の方向にスライドする。それにより、搬送対象物600が前方側および後方側の半導体装置100により支持される。その後、図19(d)に示すように、後方側の半導体装置100が矢印×4で示すようにスライドする。それにより、搬送対象物600が前方側の半導体装置100が矢印×5で示すようにスライドする。それにより、搬送対象物600は矢印×2で示すように移動する。

[0094]

このようにして、図19に示すアクチュエータにより搬送対象物600を搬送することができる。図11の半導体装置100を用いて同様のアクチュエータを構成することができる。

[0095]

また、図1および図11の半導体装置100は、光学スイッチ、光スキャナとして用いることもできる。

[0096]

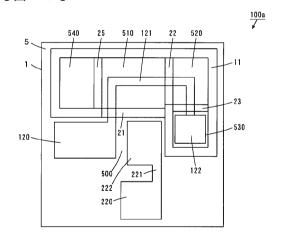

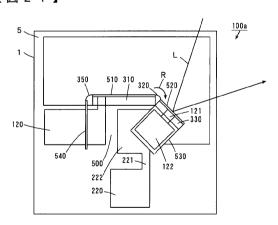

図20は本発明の第3の実施の形態に係る半導体装置の起立前の状態を示す平面図である。また、図21は本発明の第3の実施の形態に係る半導体装置の起立後の状態を示す平面図である。

[0097]

図20および図21の半導体装置100aにおいては、基板1上に図1および図11の 半導体装置100と同様の積層構造を有する。

[0098]

図20に示すように、基板1上のプレート500に谷折溝21を介して隣接するように矩形のプレート510が形成されている。プレート510の一方側に谷折溝22を介して隣接するように矩形のプレート520が形成されている。プレート520に谷折溝23を介して隣接するように矩形のプレート530が形成されている。矩形のプレート510の他方側に谷折溝25を介して隣接するようにプレート540が形成されている。

[0099]

谷折溝21を除いてプレート510,520,530,540を取り囲むように分離溝

20

30

40

50

11が形成されている。

# [0100]

プレート 5 0 0 上に静電板 2 2 2 が形成され、プレート 5 3 0 上に静電板 1 2 2 が形成されている。また、プレート 5 0 0 上に、電極パッド 1 2 0 , 2 2 0 が形成される。配線層 1 2 1 により電極パッド 1 2 0 と静電板 1 2 2 とが電気的に接続され、配線層 2 2 1 により電極パッド 2 2 0 と静電板 2 2 2 とが電気的に接続される。

#### [0 1 0 1]

第1および第2の実施の形態と同様に、プレート510,520,530,540の下方における犠牲層がエッチングにより除去されると、谷折溝21,22,23,25における歪層が図21のヒンジ310,320,350として谷状に湾曲する。それにより、図21に示すように、プレート500に対してプレート510が垂直に起立するとともに、プレート520,540もプレート500に対して垂直に起立する。また、プレート530はプレート520に対して垂直に折曲される。

# [0102]

このようにして、プレート520,530がヒンジ320を軸として回転可能かつプレート530がプレート500に対して平行移動可能に対向する。

#### [0103]

初期状態では、図21に示すように、静電板122と静電板222とが部分的に重なった状態で対向している。この状態で、電極パッド120,220を介して静電板122と静電板222との間に電圧を印加すると、静電板122と静電板222との間に静電力が働く。この場合、プレート530がヒンジ320を軸として矢印Rで示す円周方向に回動するとともにプレート500に対して平行移動し、静電板122が静電板222に完全に重なる。

#### [0104]

静電板122と静電板222との間に印加する電圧を低下させるかまたは0にすると、ヒンジ320の弾性力によりプレート530がヒンジ320を軸として矢印Rと逆の円周方向に回動するとともにプレート500に対して平行移動し、図21の状態に復帰する。

#### [0105]

このように、静電板 1 2 2 と静電板 2 2 2 との間に印加する電圧を変化させることにより、プレート 5 3 0 をヒンジ 3 2 0 を軸として円周方向に回動させるとともにプレート 5 0 0 に対して平行移動させることができる。

# [0106]

この場合、プレート520は、基板1に対して垂直な状態でヒンジ320を軸として円周方向に回動する。それにより、プレート520に光ビームLを照射すると、プレート520の回動により光ビームLの反射方向を水平面内で変化させることがでる。したがって、第3の実施の形態の半導体装置100は、光学スキャナとして用いることができる。

# [0107]

なお、上記第1~第3の実施の形態において、犠牲層3が第1の層に相当し、歪層4が第2の層に相当し、構成要素層5が第3の層に相当する。また、第1のInGaAs層41aが第1の半導体層に相当し、GaAs層42が第2の半導体層に相当し、第2のInGaAs層41bが第3の半導体層に相当する。さらに、プレート500の領域が第1の領域に相当し、プレート510,520,530の領域が第2の領域<u>の複数の領域</u>に相当する。また、ヒンジ310の領域が第1の境界部に相当し、ヒンジ320,330,340,350の領域が第2の境界部に相当する。

#### [0108]

上記第1~第3の実施の形態の半導体装置は、通常のフォトリソグラフィ、エッチング 、エピタキシャル成長等のプレーナ技術により容易かつ安価に製造することができる。

#### [0109]

上記第1~第3の実施の形態では、歪層4としてInGaAs層とGaAs層との積層構造を用いているが、これに限定されず、異なる格子定数を有する種々の半導体層の組み

合わせを用いることができる。歪層として他のIII - V族化合物半導体の積層構造、II - VI族化合物半導体の積層構造を用いてもよい。また、歪層としてSi(シリコン)およびGe(ゲルマニウム)を含む半導体層の積層構造を用いてもよい。

[0110]

また、上記第1~第3の実施の形態では、GaAsからなる基板を用いているが、犠牲層、歪層および構成要素層の材料を考慮してSi基板等の他の基板を用いてもよい。

[0111]

さらに、上記第1~第3の実施の形態では、犠牲層の材料としてA1GaAsを用いているが、これに限定されず、選択エッチングを考慮して他の材料を用いてもよい。

[0112]

10 がで

また、構成要素層の材料も上記実施の形態に限定されず、任意の材料を用いることがで きる。

【産業上の利用可能性】

[0113]

本発明は、アクチュエータ、光スイッチ、光学スキャナ等の種々の装置、素子等に利用することができる。

【図面の簡単な説明】

[0114]

【図1】本発明の第1の実施の形態における半導体装置の構成および動作を説明するための模式的断面図である。

20

30

40

- 【図2】図1の半導体装置の製造方法を示す工程図である。

- 【図3】図1の半導体装置の製造方法を示す工程図である。

- 【図4】図1の半導体装置の製造方法を示す工程図である。

- 【図5】図1の半導体装置の製造方法を示す工程図である。

- 【図6】図1の半導体装置の製造方法を示す工程図である。

- 【図7】歪層および構成要素層を示す模式的断面図である。

- 【図8】図1の半導体装置の動作原理を説明するための図である。

- 【図9】図1の半導体装置においてプレートのスライド特性を向上させるための第1の方法を示す模式的断面図である。また、

【図10】図1の半導体装置においてプレートのスライド特性を向上させるための第2の 方法を示す模式的断面図である。

【図11】本発明の第2の実施の形態における半導体装置の構成および動作を説明するための模式的断面図である。

- 【図12】図11の半導体装置の製造方法を示す工程図である。

- 【図13】図11の半導体装置の製造方法を示す工程図である。

- 【図14】図11の半導体装置の製造方法を示す工程図である。

- 【図15】図11の半導体装置の製造方法を示す工程図である。

- 【図16】図11の半導体装置の製造方法を示す工程図である。

【図17】図11の半導体装置においてプレートのスライド特性を向上させるための第1 の方法を示す模式的断面図である。

【図18】図11の半導体装置においてプレートのスライド特性を向上させるための第2の方法を示す模式的断面図である。

【図19】図1の半導体装置を用いたアクチュエータを示す模式図である。

【図20】本発明の第3の実施の形態に係る半導体装置の起立前の状態を示す平面図である。

【図21】本発明の第3の実施の形態に係る半導体装置の起立後の状態を示す平面図である。

【符号の説明】

[0115]

1 基板

- 2 バッファ層

- 3 犠牲層

- 4 歪層

- 5 構成要素層

- 1 1 分離溝

- 2 1 , 2 2 , 2 3 谷折溝

- 2 4 山折溝

- 41a 第1のInGaAs層

- 41b 第2のInGaAs層

- 4 2 GaAs層

- 100,100a 半導体装置

- 120,220 電極パッド

- 121,221 配線層

- 1 2 2 , 2 2 2 静電板

- 310,320,330,340,350 ヒンジ

- 500,510,520,530,540 プレート

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

# フロントページの続き

# (56)参考文献 特開2003-305696(JP,A)

特開2003-133583(JP,A)

特開2003-240930(JP,A)

特開2001-260092(JP,A)

特開平05-169567(JP,A)

特表2003-523833(JP,A)

特開平08-114408(JP,A)

# (58)調査した分野(Int.CI., DB名)

B81B 1/00 - 7/04

B81C 1/00 - 5/00

G02B26/08